# IRHNKC9A7130 (JANSR2N7648U3CE)

PD-97977A

Radiation Hardened Power MOSFET Surface Mount (SMD-0.5e Ceramic Lid) 100V, 35A, N-channel, R9 Superjunction Technology

#### **Features**

- Low R<sub>DS(on)</sub>

- Fast switching

- Single event effect (SEE) hardened

- Low total gate charge

- Simple drive requirements

- Hermetically sealed

- Ceramic package

- · Light weight

- Enhanced Surface mount package for direct-to-PCB mounting

- ESD rating: class 2 per MIL-STD-750, Method 1020

## **Potential Applications**

- DC-DC converter

- Motor drives

- Electric propulsion

## **Product Validation**

Qualified according to MIL-PRF-19500 for space applications

# **Description**

IR HiRel R9 technology provides superior power MOSFETs for space applications. These devices have improved immunity to Single Event Effect (SEE) and have been characterized for useful performance with Linear Energy Transfer (LET) up to  $89.8 \text{MeV} \cdot \text{cm}^2/\text{mg}$ . Their combination of low  $R_{DS(on)}$  and faster switching times reduces the power losses and increases power density in today's high speed switching applications such as DC-DC converters and motor controllers. These devices retain all of the well-established advantages of MOSFETs such as voltage control, fast switching and temperature stability of electrical parameters.

# **Ordering Information**

## Table 1 Ordering options

| Part number     | Package                | Screening Level | TID Level     |

|-----------------|------------------------|-----------------|---------------|

| IRHNKC9A7130    | SMD-0.5e (Ceramic Lid) | COTS            | 100 krad (Si) |

| JANSR2N7648U3CE | SMD-0.5e (Ceramic Lid) | JANS            | 100 krad (Si) |

| IRHNKC9A3130    | SMD-0.5e (Ceramic Lid) | COTS            | 300 krad (Si) |

| JANSF2N7648U3CE | SMD-0.5e (Ceramic Lid) | JANS            | 300 krad (Si) |

### **Product Summary**

BV<sub>DSS</sub>: 100V

• I<sub>D</sub>: 35A

•  $R_{DS(on), max}$ : 34m $\Omega$

• **Q**<sub>G, max</sub>: 48nC

• **REF:** MIL-PRF-19500/775

# **IRHNKC9A7130 (JANSR2N7648U3CE)**

# **Radiation Hardened Power MOSFET Surface Mount (SMD-0.5e Ceramic Lid)**

#### **Table of contents**

## **Table of contents**

| Pote  | ential Applications                                              | 1  |

|-------|------------------------------------------------------------------|----|

|       |                                                                  |    |

| Orde  | at Applications                                                  |    |

| Table | le of contents                                                   | 2  |

| 1     | Absolute Maximum Ratings                                         | 3  |

| 2     | _                                                                |    |

| 2.1   |                                                                  |    |

| 2.2   | Source-Drain Diode Ratings and Characteristics (Pre-Irradiation) | 5  |

| 2.3   | Thermal Characteristics                                          | 5  |

| 2.4   | Radiation Characteristics                                        | 5  |

| 2.4.1 | Electrical Characteristics - Post Total Dose Irradiation         | 5  |

| 2.4.2 | Single Event Effects – Safe Operating Area                       | 6  |

| 3     | Electrical Characteristics Curves (Pre-irradiation)              | 7  |

| 4     | Test Circuits (Pre-irradiation)                                  | 11 |

| 5     |                                                                  |    |

| Revis | ision history                                                    |    |

**Absolute Maximum Ratings**

# 1 Absolute Maximum Ratings

Table 2

Absolute Maximum Ratings (Pre-Irradiation)

| Symbol                                       | Symbol Parameter                                 |               | Unit |

|----------------------------------------------|--------------------------------------------------|---------------|------|

| $I_{D1}$ @ $V_{GS} = 12V$ , $T_{C} = 25$ °C  | Continuous Drain Current                         | 35            | А    |

| $I_{D2}$ @ $V_{GS} = 12V$ , $T_{C} = 100$ °C | Continuous Drain Current                         | 22            | А    |

| $I_{DM}$ @ $T_C = 25^{\circ}C$               | Pulsed Drain Current <sup>1</sup>                | 140           | А    |

| $P_{D}$ @ $T_{C} = 25^{\circ}C$              | Maximum Power Dissipation                        | 75            | W    |

|                                              | Linear Derating Factor                           | 0.6           | W/°C |

| $V_{GS}$                                     | Gate-to-Source Voltage                           | ± 20          | V    |

| E <sub>AS</sub>                              | Single Pulse Avalanche Energy <sup>2</sup>       | 605           | mJ   |

| I <sub>AR</sub>                              | Avalanche Current <sup>1</sup>                   | 35            | А    |

| $E_{AR}$                                     | Repetitive Avalanche Energy <sup>1</sup>         | 7.5           | mJ   |

| dv/dt                                        | Peak Diode Reverse Recovery <sup>3</sup>         | 13            | V/ns |

| T <sub>J</sub><br>T <sub>STG</sub>           | Operating Junction and Storage Temperature Range | -55 to +150   | °C   |

|                                              | Lead Temperature                                 | 300 (for 5s)  |      |

|                                              | Weight                                           | 1.0 (Typical) | g    |

$<sup>^{\</sup>rm 1}$  Repetitive Rating; Pulse width limited by maximum junction temperature.

$<sup>^2</sup>$  V<sub>DD</sub> = 100V, starting T<sub>J</sub> = 25°C, L = 2.5mH, Peak I<sub>L</sub> = 22A, V<sub>GS</sub> = 20V

$<sup>^3</sup>$   $I_{SD}$   $\leq$  35A, di/dt  $\leq$  980A/ $\mu s,\,V_{DD}$   $\leq$  100V,  $T_J$   $\leq$  150°C

**Device Characteristics**

## 2 Device Characteristics

## 2.1 Electrical Characteristics (Pre-Irradiation)

Table 3 Static and Dynamic Electrical Characteristics @ T<sub>j</sub> = 25°C (Unless Otherwise Specified)

| Symbol                         | Parameter                                     | Min. | Тур. | Max. | Unit  | Test Conditions                                           |  |  |  |

|--------------------------------|-----------------------------------------------|------|------|------|-------|-----------------------------------------------------------|--|--|--|

| BV <sub>DSS</sub>              | Drain-to-Source Breakdown<br>Voltage          | 100  | _    | _    | V     | $V_{GS} = 0V, I_{D} = 1.0 \text{mA}$                      |  |  |  |

| $\Delta BV_{DSS}/\Delta T_{J}$ | Breakdown Voltage Temp.<br>Coefficient        | _    | 0.1  | _    | V/°C  | Reference to 25°C, I <sub>D</sub> = 1.0mA                 |  |  |  |

| R <sub>DS(on)</sub>            | Static Drain-to-Source On-State<br>Resistance | _    | _    | 34   | mΩ    | $V_{GS} = 12V, I_{D2} = 22A^{1}$                          |  |  |  |

| V <sub>GS(th)</sub>            | Gate Threshold Voltage                        | 2.0  | _    | 4.0  | V     |                                                           |  |  |  |

| $\DeltaV_{GS(th)}/\Delta T_J$  | Gate Threshold Voltage<br>Coefficient         | _    | -8.9 | _    | mV/°C | $V_{DS} \ge V_{GS}$ , $I_D = 1mA$                         |  |  |  |

| Gfs                            | Forward Transconductance                      | 14   | _    | _    | S     | $V_{DS} = 15V$ , $I_{D2} = 22A^{1}$                       |  |  |  |

|                                | Zava Cata Valta aa Duain Cuurant              | _    | _    | 1.0  | ^     | $V_{DS} = 80V, V_{GS} = 0V$                               |  |  |  |

| $I_{DSS}$                      | Zero Gate Voltage Drain Current               | _    | _    | 10   | μΑ    | $V_{DS} = 80V, V_{GS} = 0V, T_{J} = 125^{\circ}C$         |  |  |  |

| I <sub>GSS</sub>               | Gate-to-Source Leakage Forward                | _    | _    | 100  | A     | V <sub>GS</sub> = 20V                                     |  |  |  |

|                                | Gate-to-Source Leakage Reverse                | _    | _    | -100 | nA    | V <sub>GS</sub> = -20V                                    |  |  |  |

| Q <sub>G</sub>                 | Total Gate Charge                             | _    | _    | 48   |       | I <sub>D1</sub> = 35A                                     |  |  |  |

| $Q_{GS}$                       | Gate-to-Source Charge                         | _    | _    | 25   | nC    | $V_{DS} = 50V$                                            |  |  |  |

| $Q_{GD}$                       | Gate-to-Drain ('Miller') Charge               | _    | _    | 9.0  |       | $V_{GS} = 12V$                                            |  |  |  |

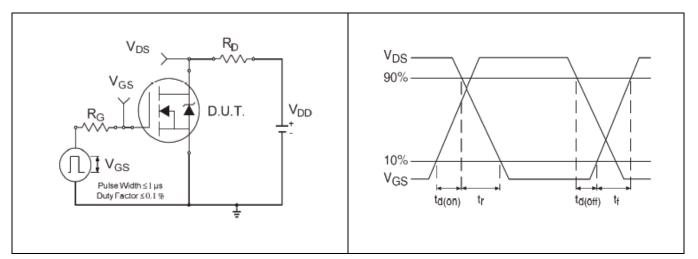

| t <sub>d(on)</sub>             | Turn-On Delay Time                            | _    | _    | 25   |       | I <sub>D1</sub> = 35A **                                  |  |  |  |

| t <sub>r</sub>                 | Rise Time                                     | _    | _    | 56   | ]     | $V_{DD} = 50V$                                            |  |  |  |

| t <sub>d(off)</sub>            | Turn-Off Delay Time                           | _    | _    | 38   | ns    | $R_G = 7.5\Omega$                                         |  |  |  |

| t <sub>f</sub>                 | Fall Time                                     |      | _    | 27   |       | $V_{GS} = 12V$                                            |  |  |  |

| $L_s + L_D$                    | Total Inductance                              | _    | 4.0  | _    | nH    | Measured from center of Drain pad to center of Source pad |  |  |  |

| C <sub>iss</sub>               | Input Capacitance                             | _    | 1800 | _    |       | $V_{GS} = 0V$                                             |  |  |  |

| C <sub>oss</sub>               | Output Capacitance                            | _    | 440  | _    | pF    | V <sub>DS</sub> = 25V                                     |  |  |  |

| C <sub>rss</sub>               | Reverse Transfer Capacitance                  |      | 3.3  | _    |       | f = 1.0 MHz                                               |  |  |  |

| R <sub>G</sub>                 | Gate Resistance                               | _    | 1.0  | _    | Ω     | f = 1.0MHz, open drain                                    |  |  |  |

<sup>\*\*</sup> Switching speed maximum limits are based on manufacturing test equipment and capability.

$<sup>^{1}</sup>$  Pulse width  $\leq$  300  $\mu s;$  Duty Cycle  $\leq$  2%

**Device Characteristics**

## 2.2 Source-Drain Diode Ratings and Characteristics (Pre-Irradiation)

Table 4 Source-Drain Diode Characteristics

| Symbol          | Parameter                                       | Min.                                                                      | Тур. | Max. | Unit | <b>Test Conditions</b>                        |  |

|-----------------|-------------------------------------------------|---------------------------------------------------------------------------|------|------|------|-----------------------------------------------|--|

| Is              | Continuous Source Current (Body Diode)          | _                                                                         | _    | 35   | Α    |                                               |  |

| I <sub>SM</sub> | Pulsed Source Current (Body Diode) <sup>1</sup> | _                                                                         | 1    | 140  | Α    |                                               |  |

| $V_{SD}$        | Diode Forward Voltage                           | _                                                                         | 1    | 1.2  | V    | $T_J = 25$ °C, $I_S = 35A$ , $V_{GS} = 0V^2$  |  |

| t <sub>rr</sub> | Reverse Recovery Time                           | _                                                                         | 140  | 210  | ns   | $T_J = 25$ °C, $I_F = 35A$ , $V_{DD} \le 25V$ |  |

| Qrr             | Reverse Recovery Charge                         | _                                                                         | 820  | _    | nC   | di/dt = 100A/μs                               |  |

| t <sub>on</sub> | Forward Turn-On Time                            | Intrinsic turn-on time is negligible (turn-on is dominated by $L_S+L_D$ ) |      |      |      |                                               |  |

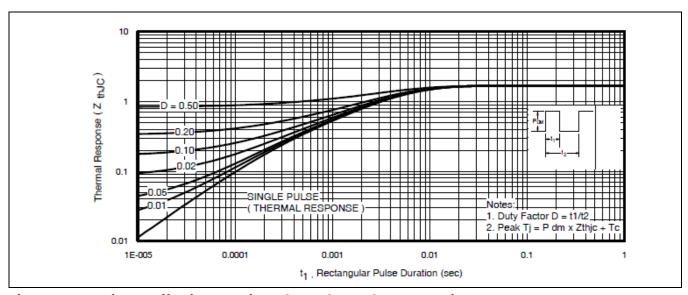

#### 2.3 Thermal Characteristics

Table 5 Thermal Resistance

| Symbol         | Parameter        | Min. | Тур. | Max. | Unit |

|----------------|------------------|------|------|------|------|

| $R_{	heta JC}$ | Junction-to-Case | _    | _    | 1.67 | °C/W |

#### 2.4 Radiation Characteristics

IR HiRel radiation hardened MOSFETs are tested to verify their radiation hardness capability. The hardness assurance program at IR HiRel is comprised of two radiation environments. Every manufacturing lot is tested for total ionizing dose (per notes 3 and 4) using the TO-3 package. Both pre- and post-irradiation performance are tested and specified using the same drive circuitry and test conditions in order to provide a direct comparison.

#### 2.4.1 Electrical Characteristics - Post Total Dose Irradiation

Table 6 Electrical Characteristics @ T<sub>j</sub> = 25°C, Post Total Dose Irradiation <sup>3, 4</sup>

| Cl                  | B                                                                              | Up to 300 | krads (Si)⁵ | 11   | T 6                               |  |

|---------------------|--------------------------------------------------------------------------------|-----------|-------------|------|-----------------------------------|--|

| Symbol              | Parameter                                                                      | Min.      | Max.        | Unit | Test Conditions                   |  |

| BV <sub>DSS</sub>   | Drain-to-Source Breakdown Voltage                                              | 100       | _           | V    | $V_{GS} = 0V$ , $I_D = 1mA$       |  |

| V <sub>GS(th)</sub> | Gate Threshold Voltage                                                         | 2.0       | 4.0         | V    | $V_{DS} \ge V_{GS}$ , $I_D = 1mA$ |  |

| $I_{GSS}$           | Gate-to-Source Leakage Forward                                                 | _         | 100         | A    | V <sub>GS</sub> = 20V             |  |

|                     | Gate-to-Source Leakage Reverse                                                 | _         | -100        | nA   | V <sub>GS</sub> = -20V            |  |

| I <sub>DSS</sub>    | Zero Gate Voltage Drain Current                                                | _         | 1.0         | μΑ   | $V_{DS} = 80V, V_{GS} = 0V$       |  |

| R <sub>DS(on)</sub> | Static Drain-to-Source On-State Resistance (TO-3) <sup>2</sup>                 |           | 36          | mΩ   | $V_{GS} = 12V, I_{D2} = 22A$      |  |

| R <sub>DS(on)</sub> | Static Drain-to-Source On-State Resistance (SMD-0.5e Ceramic Lid) <sup>2</sup> |           | 34          | mΩ   | $V_{GS} = 12V, I_{D2} = 22A$      |  |

| $V_{SD}$            | Diode Forward Voltage                                                          | _         | 1.2         | V    | $V_{GS} = 0V, I_F = 35A$          |  |

<sup>&</sup>lt;sup>1</sup> Repetitive Rating; Pulse width limited by maximum junction temperature.

$<sup>^2</sup>$  Pulse width  $\leq$  300  $\mu$ s; Duty Cycle  $\leq$  2%

$<sup>^3</sup>$  Total Dose Irradiation with V<sub>GS</sub> Bias. V<sub>GS</sub> = 12V applied and V<sub>DS</sub> = 0 during irradiation per MIL-STD-750, Method 1019, condition A.

$<sup>^4</sup>$  Total Dose Irradiation with  $V_{DS}$  Bias.  $V_{DS}$  = 80V applied and  $V_{GS}$  = 0 during irradiation per MlL-STD-750, Method 1019, condition A.

<sup>&</sup>lt;sup>5</sup> Part numbers IRHNKC9A7130 (JANSR2N7648U3CE), and IRHNKC9A3130 (JANSF2N7648U3CE)

**Device Characteristics**

# 2.4.2 Single Event Effects - Safe Operating Area

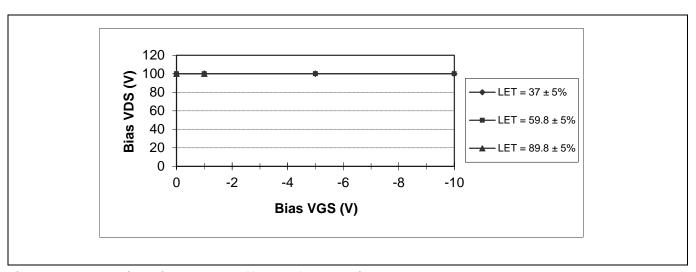

IR HiRel radiation hardened MOSFETs have been characterized in heavy ion environment for Single Event Effects (SEE). Single Event Effects characterization is illustrated in Fig. 1 and Table 7.

Table 7 Typical Single Event Effects Safe Operating Area

| LET          | Energy      | Range     |                      | V <sub>DS</sub>       | (V)                   |                        |

|--------------|-------------|-----------|----------------------|-----------------------|-----------------------|------------------------|

| (MeV·cm²/mg) | (MeV)       | (μm)      | V <sub>GS</sub> = 0V | V <sub>GS</sub> = -1V | V <sub>GS</sub> =- 5V | V <sub>GS</sub> = -10V |

| 37 ± 5%      | 417 ± 7.5%  | 50 ± 7.5% | 100                  | 100                   | 100                   | 100                    |

| 59.8 ± 5%    | 753 ± 7.5%  | 60 ± 7.5% | 100                  | 100                   | 100                   | 100                    |

| 89.8 ± 5%    | 1515 ± 7.5% | 82 ± 7.5% | 100                  | 100                   | _                     | _                      |

Figure 1 Typical Single Event Effect, Safe Operating Area

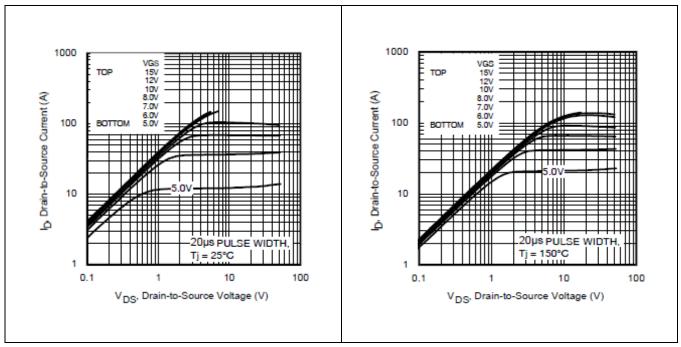

Figure 2 Typical Output Characteristics Figure 3 Typical Output Characteristics

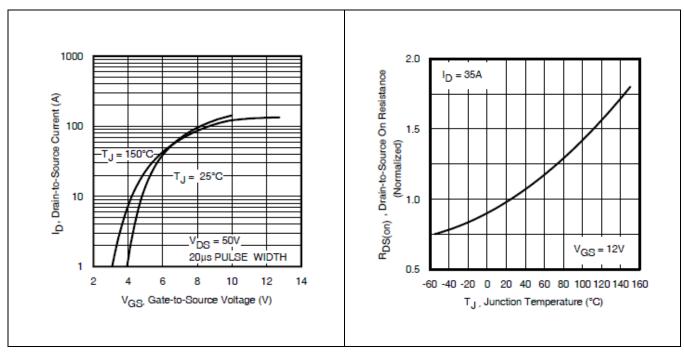

Figure 4 Typical Transfer Characteristics Figure 5 Normalized On-Resistance Vs.

Temperature

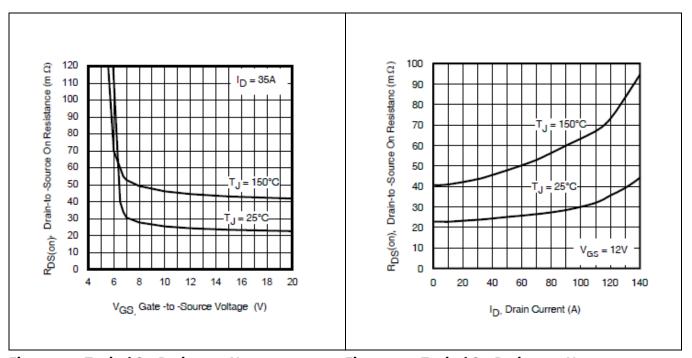

Figure 6 Typical On-Resistance Vs.

Gate Voltage

Figure 7 Typical On-Resistance Vs.

Drain Current

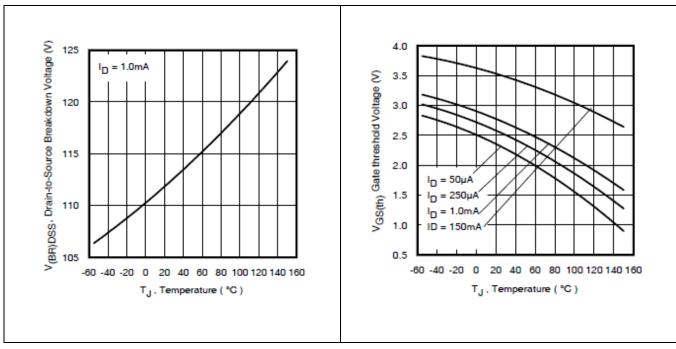

Figure 8 Typical Drain-to-Source Breakdown Voltage Vs. Temperature

Figure 9 Typical Threshold Voltage Vs.

Temperature

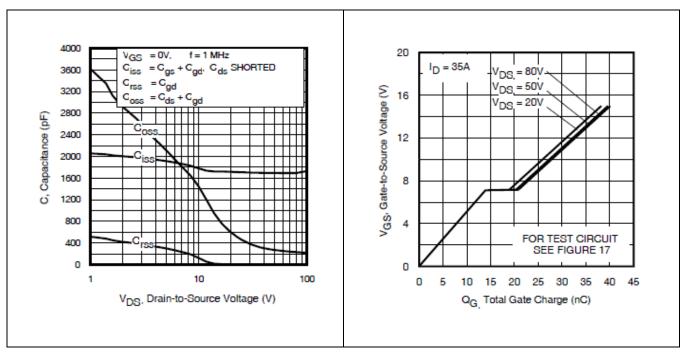

Figure 10 Typical Capacitance Vs.

Drain-to-Source Voltage

Figure 11 Typical Gate Charge Vs.

Gate-to-Source Voltage

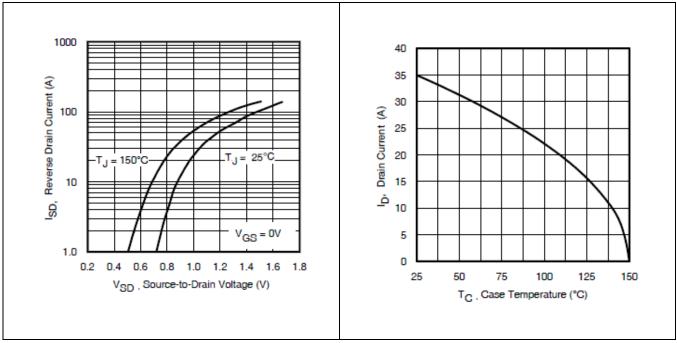

Figure 12 Typical Source-Drain Vs.

Diode Forward Voltage

Figure 13 Maximum Drain Current Vs. Case Temperature

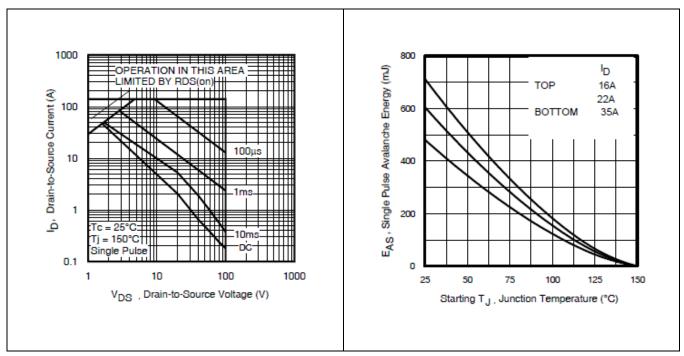

Figure 14 Maximum Safe Operating Area

Figure 15 Maximum Avalanche Energy Vs.

Junction Temperature

Figure 16 Maximum Effective Transient Thermal Impedance, Junction-to-Case

**Test Circuits (Pre-irradiation)**

# 4 Test Circuits (Pre-irradiation)

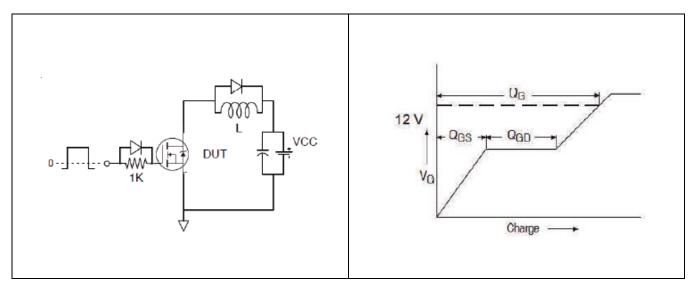

Figure 17 Gate Charge Test Circuit

Figure 18 Gate Charge Waveform

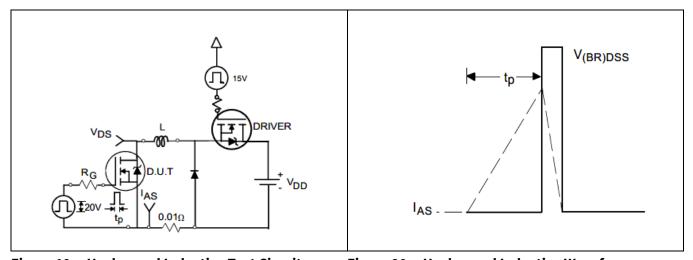

Figure 19 Unclamped Inductive Test Circuit

Figure 20 Unclamped Inductive Waveform

Figure 21 Switching Time Test Circuit

Figure 22 Switching Time Waveforms

Package outline

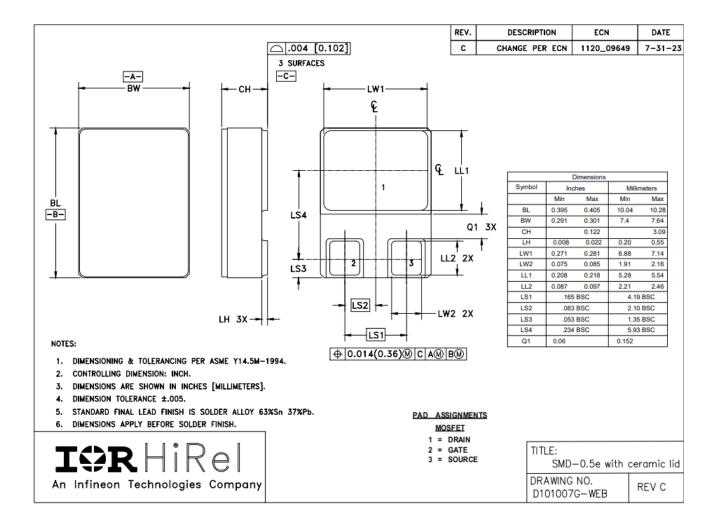

# 5 Package outline

Note: For the most updated package outline, please see the website: **SMD-0.5e with Ceramic Lid**

# IRHNKC9A7130 (JANSR2N7648U3CE) Radiation Hardened Power MOSFET Surface Mount (SMD-0.5e Ceramic Lid)

# **Revision history**

# **Revision history**

| Document<br>version | Date of release | Description of changes                            |

|---------------------|-----------------|---------------------------------------------------|

|                     | 11/13/2023      | Preliminary datasheet with PPD number (PPD-97977) |

| Rev A               | 12/05/2023      | Final datasheet with PD number                    |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2023-12-05

**Published by**

International Rectifier HiRel Products, Inc.

An Infineon Technologies company El Segundo, California 90245 USA

© 2023 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

**Document reference**

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest International Rectifier HiRel Products, Inc., an Infineon Technologies company, office.

International Rectifier HiRel Components may only be used in life-support devices or systems with the expressed written approval of International Rectifier HiRel Products, Inc., an Infineon Technologies company, if failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety and effectiveness of that device or system.

Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.